### EXPLICACION DE LAS DIFERENCIAS TRANSFER AC-DC DE VOLTAJE EN CONVERSORES TERMICOS FABRICADOS SOBRE UN CHIP DE SILICIO A ALTAS FRECUENCIAS

L. Scarioni (1), M. Klonz (2)

- (1) Universidad de Carabobo, Facultad de Ciencias y Tecnología, Departamento de Física, Valencia, Venezuela. Iscarion@uc.edu.ve

- (2) Physikalisch-Technische Bundesanstalt (PTB), Bundesallee 100, 38116 Braunschweig, Germany.

Manfred.Klonz@ptb.de

Resumen: Se ha encontrado una explicación para las diferencias transfer ac-dc de voltaje sobre 100 kHz del conversor térmico de multiuniones de películas delgadas estándar (PMJTC) desarrollado en el PTB, fabricado sobre un chip de silicio. El modelo desarrollado para la simulación indica que el acoplamiento capacitivo entre los puntos de contacto del calefactor da origen a una resonancia cuando la resistencia del calefactor se incrementa, incrementando de esta manera la diferencia transfer ac-dc a valores negativos. De acuerdo al modelo se puede mejorar la respuesta en frecuencia de los conversores térmicos fabricados sobre un chip de silicio, reduciendo el tamaño de los puntos de contacto y utilizando sustratos con una constante dieléctrica más pequeña que la correspondiente al silicio.

#### 1. INTRODUCCION

Los conversores térmicos de multiuniones de películas delgadas (PMJTCs) sobre un chip de silicio fueron desarrollados en el Physikalisch-Technische Bundesanstalt (PTB) in 1986 [1].

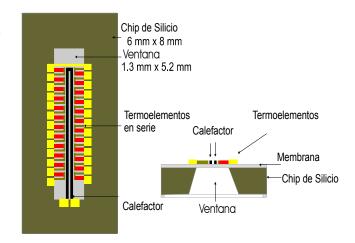

El diseño básico se muestra en la Fig.1. En el PTB-PMJTC sobre un chip de silicio, un calefactor de películas delgadas de forma bifilar es fabricado mediante "sputtering" y un arreglo de 100 termoelementos es evaporado sobre una membrana de Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>. La junta caliente de los termoelementos está colocada a lo largo del calefactor y las juntas frías están simétricamente colocadas sobre el borde de silicio, actuando como un sumidero de calor. La membrana delgada dieléctrica y el arreglo de los termoelementos proporcionan una baja conductancia térmica, lo cual da al dispositivo una alta sensibilidad.

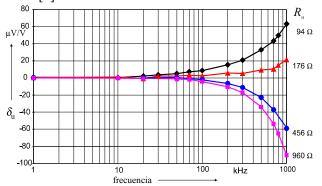

Para aplicaciones a bajas frecuencias, la constante de tiempo térmica del PMJTC ha sido incrementada, colocando un obelisco debajo del calefactor [2]. A altas frecuencias sobre 100 kHz, los PMJTCs fabricados con o sin obelisco muestran un incremento en la diferencia transfer ac-dc hacia valores negativos con el incremento de la resistencia del calefactor. La fuente de esta diferencia transfer ha sido atribuida inicialmente a: capacitancia entre los dos hilos del calefactor, capacitancia entre el calefactor y los termoelementos y pérdidas dieléctricas en la membrana. Sin embargo, los valores calculados son tan pequeños que no explican las diferencias observadas (Fig. 2).

Fig. 1 PTB-PMJTC sobre un chip de silicio

### 2. ANALISIS DE LA DIFERENCIA AC-DC EN PMJTCs SOBRE UN CHIP DE SILICIO

Diferentes modelos han tratado de explicar las grandes diferencias ac-dc en los PMJTCs sobre chip de Silicio que se observan para valores grandes de la resistencia del calefactor. El obelisco de silicio debajo del calefactor ha sido detectado por Wunsch [3] como una fuente de diferencia ac-dc negativa. El obelisco de silicio debajo del calefactor incrementa la capacitancia en paralelo con el calefactor y así la diferencia transfer ac-dc hacia valores negativos. Pero la mayor parte de la diferencia ac-dc es también observada en PMJTCs sin obelisco (Fig . 2).

- El efecto tiene las siguientes características:

- 1) es independiente del voltaje de entrada,

- 2) depende fuertemente del valor de la resistencia del calefactor,

- 3) se incrementa cuadráticamente con la frecuencia.

Sin embrago este efecto no es observado en dispositivos con una configuración del calefactor recta [4].

Fig. 2. Mediciones de diferencias transfer ac-dc  $\delta_u$  a altas frecuencias de PMJTCs, sin obelisco para diferentes resistencias del calefactor  $R_H$ .

# 3. INFLUENCIA DEL ACOPLAMIENTO CAPACITIVO

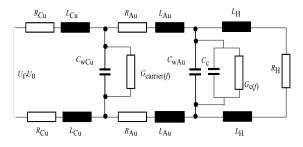

La influencia del acoplamiento capacitivo fue estudiada fabricando dos grupos de PMJTCs con el obelisco de silicio, diferentes resistencias del calefactor y con grandes y pequeños puntos de contacto (pads) del calefactor. El área de los puntos de contacto se incremento en un factor de 23, dando como resultado una capacitancia de 10,8 pF en lugar de 1,7 pF. El modelo parametrico mostrado en la Fig. 3 fue utilizado para determinar la ac-dc diferencia transfer debido al acoplamiento capacitivo entre los puntos de contacto del calefactor.

Fig. 3 Modelo parametrico del calefactor con el acoplamiento capacitivo  $C_c=1.7$  pF,  $C_{wCu}=0.7$  pF,  $C_{wAu}=0.07$  pF,  $G_{carrier}=4.4$  nS y  $G_c=53.4$  nS a 1 MHz respectivamente,  $R_{Cu}=1$  m $\Omega$ ,  $R_{Au}=5$  m $\Omega$ , y la inductancia de ambos  $L_{Cu}=1$  nH and  $L_{Au}=5$  nH.

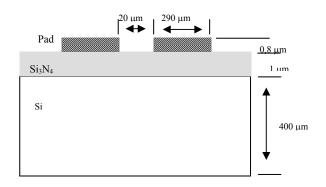

La Fig. 4 muestra los parámetros utilizados en el cálculo del acoplamiento capacitivo. Este cálculo fue realizado modelando los pads como una guía de onda coplanar simétrica [6].

Fig. 4. Parámetros geométricos para el cálculo del acoplamiento capacitivo en los pads del calefactor.

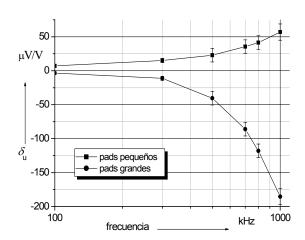

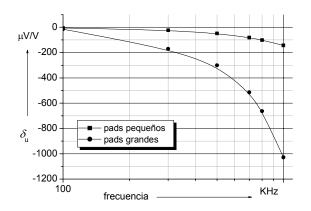

Las Figs. 5 y 6 muestran las mediciones de la diferencia transfer ac-dc para PMJTCs con obelisco y diferentes resistencias del calefactor.

Fig. 5 Mediciones de la diferencia transfer ac-dc para un PMJTC con obelisco, con grandes y pequeños puntos de contacto (pads) del calefactor. Resistencia del calefactor  $R_H$  = 112  $\Omega$ .

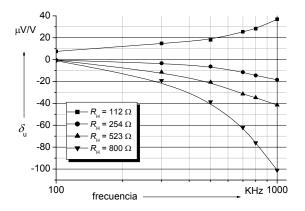

La Fig. 7 muestra los valores calculados de la diferencia transfer ac-dc de acuerdo al modelo presentado en la Fig. 3, debido al acoplamiento capacitivo, para diferentes resistencias del calefactor.

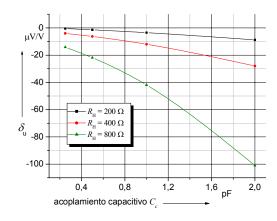

La Fig. 8 muestra la variación de los valores calculados de la diferencia transfer ac-dc con la capacitancia de los puntos de contacto (pads) del calefactor para diferentes resistencias.

Fig. 6 Mediciones de la diferencia transfer ac-dc para un PMJTC con obelisco, con grandes y pequeños puntos de contacto (pads) del calefactor. Resistencia del calefactor  $R_H$  = 800  $\Omega$

Fig. 7 Valores Calculados de las diferencias transfer ac-dc debido al acoplamiento capacitivo en los pads del calefactor para diferentes resistencias del calefactor.

## 4. MODELO UTILIZADO PARA LA SIMULACION

El modelo utilizado para el calculo de la diferencia transfer ac-dc del PMJTC sobre un chip de Silicio en el rango de frecuencias de 100 kHz a 1 MHz es:

$$\delta_{\text{Uac-dc}} = \delta_{\text{U1}} + \delta_{\text{U2}} + \delta_{\text{U3}} \qquad (1)$$

donde

$\delta_{\text{U1}}$ = diferencia transfer debido al cambio en la parte real de la impedancia del calefactor con el obelisco,

$\delta_{\text{U2}}$ = diferencia transfer debido a capacitancias entre los hilos de conexión y al acoplamiento capacitivo,

$\delta_{\rm U3}$ = diferencia transfer debido al efecto Skin en los hilos de conexión.

Fig. 8 Variación de las diferencias transfer ac-dc calculadas con la capacitancia de los puntos de contacto del calefactor para diferentes resistencias  $R_{\rm H}$ .

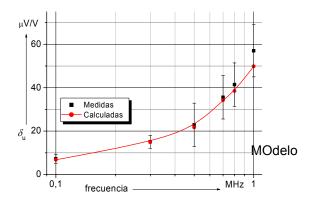

La Fig.9 muestra los valores medidos y los valores calculados según el modelo presentado en la Eq. (1) para un PMJTC con obelisco de Silicio, pads pequeños y una resistencia del calefactor de 112  $\Omega$ .

Fig. 9 Valores medidos y valores calculados según el modelo presentado en la Eq. (1) para un PMJTC con obelisco de Silicio, pequeños pads y una resistencia del calefactor de 112  $\Omega$ .

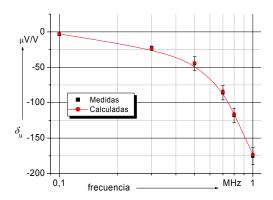

La Fig.10 muestra los valores medidos y los valores calculados según el modelo presentado en la Eq. (1) para un PMJTC con obelisco de Silicio, pads grandes y una resistencia del calefactor de 112  $\Omega$ .

Fig. 10 Valores medidos y valores calculados según el modelo presentado en la Eq. (1) para un PMJTC con obelisco de Silicio, pads grandes y una resistencia del calefactor de 112  $\Omega$ .

### 5. CONCLUSIÓN

Los experimentos y los cálculos realizados del efecto del acoplamiento capacitivo de los puntos de contacto del calefactor del PTB-PMJTC, muestran un incremento de la diferencia transfer ac-dc a valores negativos con el incremento de la frecuencia y de la resistencia del calefactor. Mejoras en la respuesta a alta frecuencia de los PTB-PMJTCs se pueden conseguir con una disminución de la capacitancia de los puntos de contacto del calefactor. Esto se obtiene con una disminución del tamaño de los puntos de contacto (pads) o con el uso de sustratos con una permitividad más pequeña que la del silicio, como por ejemplo, el cuarzo. El modelo utilizado también permite calcular la influencia del obelisco de silicio debajo del calefactor.

#### **REFERENCIAS**

- [1] M. Klonz, T. Weimann, "Accurate Thin Film Multi-junction Thermal Converter on a Silicon Chip," *IEEE <u>Trans. Instrum. Meas.</u>*, vol. 38, pp 335-339, April 1989.

- [2] M . Klonz, T. Weimann, "Increasing the Time constant of Thin-Film Multijunction Thermal Converters at PTB/ IPHT," <u>IEEE</u>

- <u>Trans. Instrum. Meas.</u>, vol. 40, no.2, pp 350-351, April 1991.

- [3] T. Wunsch, "Microfabricated Multiunction Thermal Converters," Ph.D. Engineering, The University of New Mexico, July 2001.

- [4] T. Wunsch, J. Kinard, R. Manginell, O. Solomon, and T. Lipe, "Fabrication process for planar Thin-Film Multijunction Thermal Converters," in *CPEM Conf. Dig. 2000*, pp 387-388, May 2000.

- [5] L. Scarioni, M. Klonz, H. Laiz and M. Kampik, "High-Frequency Thin-Film Multijunction Thermal Converter on a Quartz Crystal Chip," *IEEE Trans. Instrum. Meas.*, vol. 52, no.2, pp 345-349, April 2003.

- [6] B. C. Wadell, "Transmission Line," Design Handbook, Artech House, Inc., 1991.